CMOSロジックの電圧閾値VIL, VIH, VOL, VOHの謎を解き明かす

デジタル回路の安定動作に不可欠な、これらの電圧パラメータを徹底解説します。

CMOS(Complementary Metal-Oxide-Semiconductor)技術は、現代のデジタル集積回路(IC)の主流となっています。これらの回路が正しく論理レベル(HIGHまたはLOW)を認識し、出力するためには、特定の電圧基準が不可欠です。この基準となるのが、VIL (入力LOW電圧)、VIH (入力HIGH電圧)、VOL (出力LOW電圧)、VOH (出力HIGH電圧) といったパラメータです。これらを理解することは、デジタルシステムの設計、デバッグ、そして異なるIC間の互換性を確保する上で極めて重要です。

主要なポイント

- VIL (入力LOW電圧): デジタル入力が論理LOWとして確実に認識される最大の電圧レベルです。

- VIH (入力HIGH電圧): デジタル入力が論理HIGHとして確実に認識される最小の電圧レベルです。

- VOL (出力LOW電圧): デジタル出力が論理LOWを示す際に取り得る最大の電圧レベルです。

- VOH (出力HIGH電圧): デジタル出力が論理HIGHを示す際に取り得る最小の電圧レベルです。

VIL, VIH, VOL, VOH とは何か?

これらの電圧レベルは、デジタルICが信号をどのように解釈し、生成するかを定義する基本的な仕様です。各パラメータについて詳しく見ていきましょう。

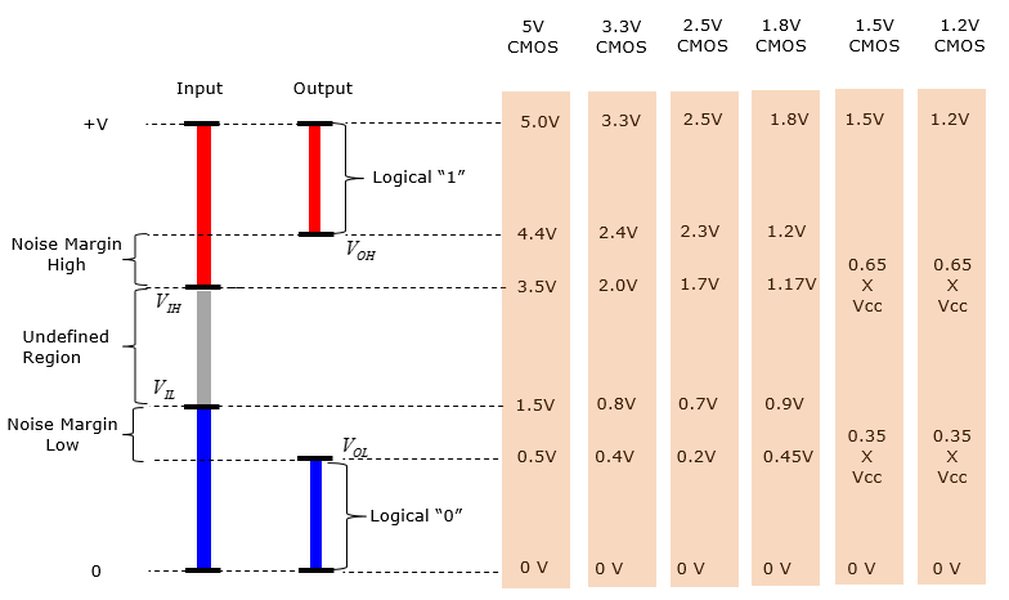

CMOSロジックにおける入力および出力電圧レベルの概念図。

入力電圧レベル: VIL と VIH

VIL (Maximum Input Low Voltage) - 入力LOW電圧

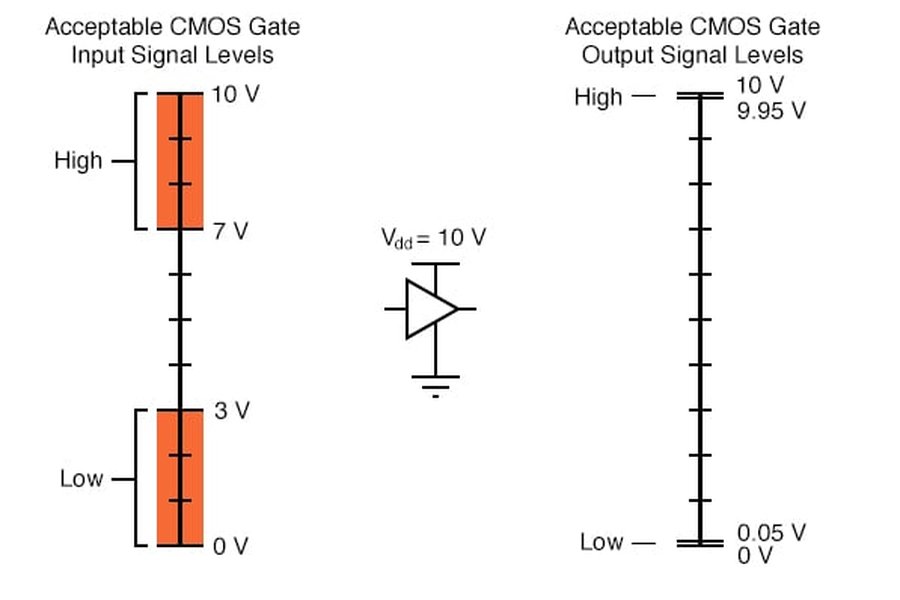

VILは、ICの入力端子が論理「LOW」(または「0」)として確実に認識する最大の入力電圧です。入力信号の電圧がVIL以下であれば、ICはその入力をLOW状態として解釈します。例えば、あるICのVILが0.8Vの場合、0Vから0.8Vまでの入力電圧はLOWとして扱われます。

VIH (Minimum Input High Voltage) - 入力HIGH電圧

VIHは、ICの入力端子が論理「HIGH」(または「1」)として確実に認識する最小の入力電圧です。入力信号の電圧がVIH以上であれば、ICはその入力をHIGH状態として解釈します。例えば、あるICのVIHが2.0Vの場合、2.0V以上の入力電圧はHIGHとして扱われます。

不確定領域 (Undefined Region)

VILとVIHの間には「不確定領域」または「遷移領域」と呼ばれる電圧範囲が存在します。入力電圧がこの範囲内にある場合、ICがその入力をHIGHとLOWのどちらとして解釈するかは保証されず、不安定な動作や誤動作を引き起こす可能性があります。したがって、設計においては入力信号がこの不確定領域に長時間留まらないように注意する必要があります。

出力電圧レベル: VOL と VOH

VOL (Maximum Output Low Voltage) - 出力LOW電圧

VOLは、ICが出力端子から論理「LOW」を送り出す際に、その出力電圧が超えない最大の電圧です。理想的には0Vですが、実際にはトランジスタの特性によりわずかな電圧(数十ミリボルトから数百ミリボルト程度)が発生します。例えば、VOLが0.4Vの場合、ICがLOWを出力するときの電圧は0.4V以下に保証されます。

VOH (Minimum Output High Voltage) - 出力HIGH電圧

VOHは、ICが出力端子から論理「HIGH」を送り出す際に、その出力電圧が下回らない最小の電圧です。理想的には電源電圧VDDですが、実際には内部の電圧降下によりVDDよりもわずかに低い電圧となります。例えば、電源電圧が5VでVOHが4.5Vの場合、ICがHIGHを出力するときの電圧は4.5V以上に保証されます。

これらの電圧レベルの重要性

VIL, VIH, VOL, VOHは、デジタルシステムが安定して動作するために不可欠な要素です。特に、異なるIC間で信号をやり取りする際の互換性を保証し、ノイズに対する耐性を確保する上で重要な役割を果たします。

ノイズマージン (Noise Margin)

ノイズマージンは、システムが信号経路上の電気的ノイズ(電圧変動や干渉)によって誤動作することなく、正しく論理レベルを伝達できる「余裕」を示します。ノイズマージンには、HIGHレベルノイズマージン (NMH) とLOWレベルノイズマージン (NML) の2種類があります。

- HIGHレベルノイズマージン (NMH): \( NM_H = V_{OH_{min}} - V_{IH_{min}} \)

- LOWレベルノイズマージン (NML): \( NM_L = V_{IL_{max}} - V_{OL_{max}} \)

あるICの出力が別のICの入力に接続される場合、出力側のVOHは入力側のVIHよりも十分に高く、出力側のVOLは入力側のVILよりも十分に低い必要があります ( \(V_{OH} > V_{IH}\) かつ \(V_{OL} < V_{IL}\) )。この差がノイズマージンとなり、この値が大きいほど、ノイズに対する耐性が高くなります。CMOSロジックは一般的にTTLなどの他のロジックファミリーと比較して、広いノイズマージンを持つという特徴があります。

論理レベルとノイズマージンの関係を示す図。

IC間の互換性

異なるメーカーのICや、異なるロジックファミリー(例:CMOSとTTL)、あるいは異なる電源電圧で動作するICを接続する場合、これらの電圧レベルの互換性を確認することが極めて重要です。出力側のVOH/VOLが、入力側のVIH/VILの仕様を満たしていない場合、信号が正しく伝達されず、システムの誤動作や故障の原因となります。このような場合、レベルシフタ(電圧レベル変換IC)の使用が必要になることがあります。

CMOS回路内部の動作と電圧レベル

CMOSロジックゲートの基本的な構成要素は、PチャネルMOSFET (PMOS) とNチャネルMOSFET (NMOS) です。これらのトランジスタが相補的に動作することで、低消費電力で明確な出力電圧レベルを実現します。

- 入力がHIGHレベル(VIH以上、通常はVDDに近い電圧)の場合:NMOSトランジスタがオンになり、PMOSトランジスタがオフになります。これにより、出力はグラウンド(GND、0V)に接続され、論理LOW(VOLに近い電圧)が出力されます。

- 入力がLOWレベル(VIL以下、通常はGNDに近い電圧)の場合:PMOSトランジスタがオンになり、NMOSトランジスタがオフになります。これにより、出力は電源電圧(VDD)に接続され、論理HIGH(VOHに近い電圧)が出力されます。

CMOSの入力しきい値電圧は、PMOSとNMOSのしきい値電圧のバランスによって決定され、一般的に電源電圧VDDのおよそ30%~70%の範囲に設定されます。

代表的なCMOS電圧レベルとデータシートの確認

VIL, VIH, VOL, VOHの具体的な値は、使用するICの種類、電源電圧、温度条件などによって異なります。そのため、常に個々のICのデータシートを参照して、正確な仕様を確認する必要があります。

以下は、一般的なCMOSロジックICにおける電圧レベルの目安です。

| パラメータ | 記号 | 説明 | 5V CMOS (代表例) | 3.3V CMOS (代表例) |

|---|---|---|---|---|

| 入力LOW電圧 | VIL | 入力を「0」と認識する最大電圧 | ~1.5V (VDDの約30%) | ~0.8V - 1.0V |

| 入力HIGH電圧 | VIH | 入力を「1」と認識する最小電圧 | 3.5V~ (VDDの約70%) | ~2.0V - 2.3V |

| 出力LOW電圧 | VOL | 出力「0」の最大電圧 (GNDに近い) | ~0.1V - 0.4V | ~0.1V - 0.4V |

| 出力HIGH電圧 | VOH | 出力「1」の最小電圧 (VDDに近い) | 4.5V~ (VDDに近い) | 2.9V~ (VDDに近い) |

注: 上記の表の値は一般的な目安であり、実際の値はICのデータシートで確認してください。

TTL (Transistor-Transistor Logic) といった他のロジックファミリーと比較すると、CMOSは一般的にVOHがよりVDDに近く、VOLがよりGNDに近い電圧レベルを持つため、ノイズマージンが広い傾向にあります。ただし、異なるロジックファミリー間(例: 5V CMOSと3.3V CMOS、またはCMOSとTTL)で信号を接続する際には、これらの電圧レベルの互換性に特に注意が必要です。

Texas Instrumentsによる出力/入力ロジックレベル (VOH, VOL, VIH, VIL) の解説ビデオ。これらの電圧レベルがIC間の互換性確認にどのように役立つかを説明しています。

CMOS電圧特性の比較

以下のレーダーチャートは、異なる条件下でのCMOSロジックの主要な電圧特性(VIL, VIH, VOL, VOH)と、それらから導かれるノイズマージン(NMH, NML)を概念的に比較したものです。値は典型的な範囲を示しており、特定のデバイスのデータシート値とは異なる場合があることに注意してください。このチャートは、電源電圧や負荷条件がこれらのパラメータにどのように影響しうるか、また、それらがノイズ耐性にどう関わってくるかを視覚的に理解するのに役立ちます。

このチャートから、電源電圧が低下すると、絶対的な電圧レベル(VIL, VIH, VOL, VOH)が低くなるだけでなく、ノイズマージンも一般的に小さくなる傾向があることがわかります。これは、低電圧システムを設計する際には、ノイズ対策がより重要になることを示唆しています。

CMOS電圧レベルの概念マップ

以下のマインドマップは、CMOSロジックにおけるVIL, VIH, VOL, VOHの各パラメータと、それらに関連する主要な概念(ノイズマージン、互換性など)を視覚的に整理したものです。これにより、これらの用語がデジタル回路設計においてどのように相互に関連しているかを俯瞰的に理解することができます。

認識される最大入力電圧"] id1b["VIH (入力HIGH電圧)"] id1b1["定義: 論理HIGHとして

認識される最小入力電圧"] id1c["不確定領域"] id1c1["VIL < 電圧 < VIH

動作不安定の原因"] id2["出力レベル"] id2a["VOL (出力LOW電圧)"] id2a1["定義: 論理LOW出力時の

最大電圧"] id2b["VOH (出力HIGH電圧)"] id2b1["定義: 論理HIGH出力時の

最小電圧"] id3["重要性"] id3a["ノイズマージン"] id3a1["NMH = VOH - VIH"] id3a2["NML = VIL - VOL"] id3a3["ノイズ耐性の指標"] id3b["IC間互換性"] id3b1["VOH > VIH (受信側)"] id3b2["VOL < VIL (受信側)"] id3b3["異なるロジックファミリー

・電圧システム間の接続"] id3c["信頼性の高い信号伝達"] id4["データシート"] id4a["各ICの正確な仕様を記載"] id4b["設計時の必須確認項目"] id5["CMOS内部動作"] id5a["PMOS & NMOS トランジスタ"] id5b["入力に応じたスイッチング動作"]

このマインドマップは、CMOS電圧レベルの核心的な概念を整理し、それらがどのようにデジタル回路の堅牢な動作に寄与するかを示しています。入力側ではVILとVIHが論理状態を決定し、出力側ではVOLとVOHがその状態を外部に伝えます。これらの間の適切なマージン(ノイズマージン)が、システムの信頼性を高める鍵となります。

よくある質問 (FAQ)

推奨される関連検索

- CMOSインバータの電圧伝達特性とは何か?

- 異なるロジックレベルのICを接続する方法とは?

- デジタル回路におけるノイズ対策の重要性について知りたい。

- TTLとCMOSのロジックレベルの違いと比較について教えて。

参考文献

Last updated May 6, 2025