Understanding Memory Operations in Computer Architecture

A detailed overview of MAR and MDR functions during a memory read operation

Key Highlights

- MAR Functionality: The Memory Address Register holds the binary address of the target memory location.

- MDR Role: The Memory Data Register temporarily stores the data that is read from memory.

- Read Operation Process: The read cycle involves setting the MAR, fetching data from memory to the MDR, and then handing the data off to the CPU for processing.

Detailed Analysis of the Read Operation

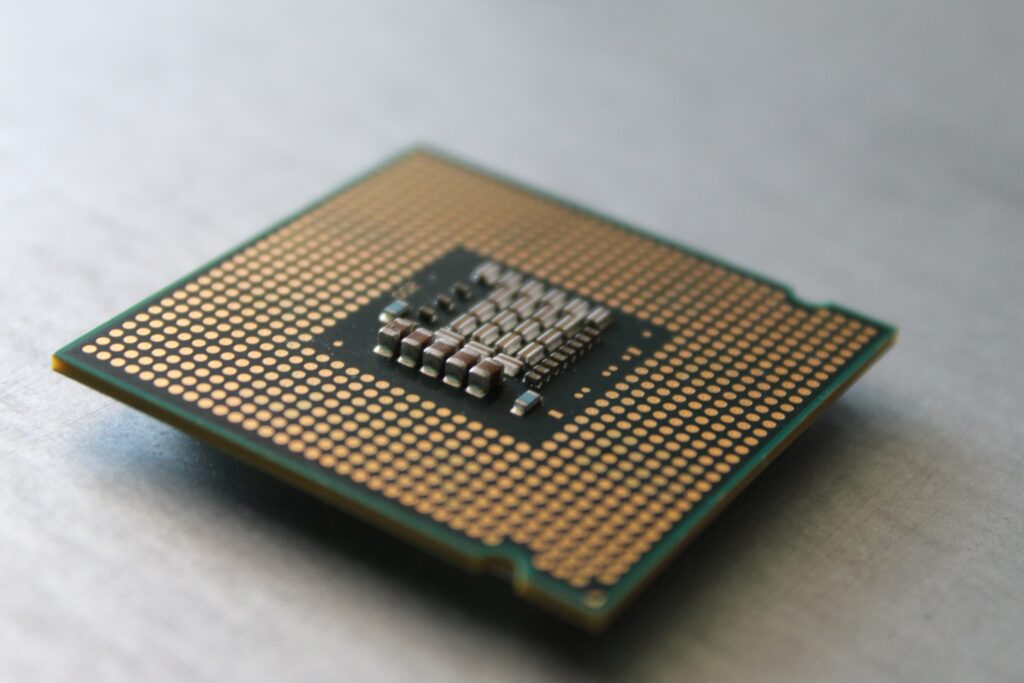

Memory operations in computer architecture are fundamental to effective data processing. In particular, understanding the role of the Memory Address Register (MAR) and the Memory Data Register (MDR) can elucidate how data flows from memory to the CPU during a read operation. When addressing the specific case where the contents of memory location 1000 0001 are read as 0101 001, both registers play distinct yet interlinked roles in this process.

Step-by-Step Operation

1. Setting Up the Memory Address Register (MAR)

The first step in a read operation involves the CPU placing the binary address of the desired memory location into the Memory Address Register (MAR). In this specific instance, the CPU needs to access data stored at address 1000 0001. This action communicates to the memory unit the exact location from which data will be retrieved. The MAR is essentially the “address poster,” declaring which memory cell is under operation.

More technically, the MAR’s primary task is to facilitate targeted data access. When a read request is initiated, the MAR holds the address 1000 0001 in its entirety. This register plays a critical role in eliminating ambiguity as it ensures that only data at the specified address is accessed, thereby maintaining the integrity of the operation.

2. Initiation of the Data Retrieval Process

After the MAR is loaded with the target address, the system’s control unit signals the memory module to begin the retrieval process. At this point, the memory system locates the data stored at address 1000 0001. The effective communication between the CPU and memory is enabled through a series of control signals that coordinate the transfer of information.

The process remains highly synchronized; the precise loading of the MAR combined with the proper dispatch of control signals ensures that data corruption or misplacement does not occur. Here, the MAR not only serves as a static placeholder for the address but also as an active participant that confirms the location for the memory module to seek.

3. Reading Data into the Memory Data Register (MDR)

Once the memory unit has identified the requested location, it retrieves the stored data. In our scenario, the data contained within memory location 1000 0001 is 0101 001. This data is then transferred into the Memory Data Register (MDR). The MDR is designed as a buffer that temporarily retains data during the transfer process between the memory and the CPU.

The significance of the MDR lies in its role as an intermediary storage site. Once the data is read from memory, it is not immediately consumed by the CPU; instead, it is held safely in the MDR. This pause in data processing allows the CPU additional time to prepare for subsequent operations, ensuring that the busy data stream is managed effectively. Think of the MDR as the holding pen where freshly fetched data awaits further processing instructions.

4. Utilization of Retrieved Data

With the data now securely stored in the MDR, the CPU can complete the read operation. The MDR becomes the immediate source from which the CPU draws the data for further computation or for subsequent steps in a program's execution. The harmonious interaction between the MAR and the MDR, thus, bridges the gap between memory storage and CPU data processing.

More so, the precise execution of these steps underlines an essential principle in computer architecture: the separation of address and data pathways. Such a design choice is pivotal in enhancing both the efficiency and the reliability of data transfers within the system.

Tables and Visual Representation

Summarizing the above operations, it is beneficial to refer to a clear and concise table that outlines the distinct roles and the corresponding contents during the read operation:

| Register | Contents During Read Operation | Primary Function |

|---|---|---|

| Memory Address Register (MAR) | 1000 0001 | Holds the address of the memory location to be accessed |

| Memory Data Register (MDR) | 0101 001 | Temporarily stores the data fetched from the memory location |

In this table, each register is explicitly associated with its content and function during the operation. The MAR clearly points to the specific memory location by holding the address 1000 0001, while the MDR holds the fetched data 0101 001 from that location.

Determining Factors in Data Transfer

Role of System Control Signals

A critical component that supports the actions of the MAR and MDR is the system’s control unit. This control unit orchestrates the timing and sequence of the operations. It dispatches the read commands, confirms that the required address is correctly loaded into the MAR, signals memory to output data, and ensures the uninterrupted transfer of that data to the MDR.

Without such precise control, the integrity of the data transfer could be compromised. The control unit ensures that each operation phase is completed before the next begins, and that error-checking mechanisms are in place, all of which contribute significantly to system stability. This precision is paramount in modern computer systems where data must be moved rapidly and accurately.

Implications in CPU Performance

The efficiency with which the MAR and MDR perform their respective tasks directly impacts CPU performance. By ensuring that data is quickly and correctly routed from memory to the CPU, these registers minimize wait times and allow the CPU to execute instructions at optimal speed. An effective read operation also helps in maintaining a steady pipeline in the fetch-decode-execute cycle, which is essential for high-speed processing.

The design of MAR and MDR illustrates the layered approach to computer architecture where delineated responsibilities allow for specialization and optimization. In advanced computer architectures, such registers are part of a larger system of caching, buffering, and parallel data pathways designed to overcome the inherent latencies in accessing volatile memory.

Buffering and Data Alignment Considerations

The use of the MDR as a temporary storage location not only serves to hold data but also provides a buffer that can align data according to the CPU’s internal format requirements. This buffering mechanism ensures that complex data types or multi-byte values are correctly transferred and assembled once they are loaded from the memory.

The buffering process is especially important in systems where memory accesses are performed in blocks, such as in cache line transfers. The MDR effectively mediates the transition between the raw memory data and the structured format that the CPU expects, reducing the potential for misinterpretation and errors.

Expanded Discussion on Architectural Insights

Integration of MAR and MDR in Modern Systems

While the basic principles of the MAR and MDR have remained constant since their inception in early computer design, modern systems have seen these registers integrated into more complex processing architectures. In contemporary systems, similar principles apply not only to the central processing unit but also to peripheral controllers, graphics processing units (GPUs), and even network cards.

For instance, in multi-core processors where parallel processing is essential, similar register structures ensure that each core can quickly access and handle the data it needs without interference. Such efficiency is critical in environments where data throughput and real-time processing are paramount. The MAR and MDR exemplify the modular design philosophy and continue to be relevant, serving as a template for more sophisticated versions of data transfer registers.

Synchronization and Timing Issues

Synchronization during the memory access phase is another pivotal aspect where MAR and MDR come into play. The timing of how addresses and data are transferred is strictly controlled. This synchronization ensures that the CPU does not attempt to process incomplete data or access memory locations out of sequence.

The timing mechanisms are integrated within the control unit, ensuring that after the data is placed into the MDR, there is a clear signal that the data is ready for processing. In more advanced systems, clock cycles and latency optimizations play vital roles in this regard, often implemented using complex scheduling algorithms.

Hardware and Software Interplay

Both hardware and software layers must cooperate effectively to leverage the full potential of these registers. At the hardware level, the physical design of the MAR and MDR must support rapid, error-free data transfers. On the software side, system-level commands initiate these transfers and manage the synchronization, buffering, and error-correcting mechanisms.

This duality highlights an essential aspect of computer science: the integration of physical hardware design with logical software control. By understanding this interplay, engineers can optimize system performance and ensure that data flows seamlessly from memory to the CPU and between various subsystems.

Practical Implications and Further Reading

Implementing Memory Access in Educational and Professional Contexts

In educational settings, the MAR and MDR are frequently highlighted as examples of fundamental computer architecture elements. They offer a concrete representation of abstract data flow and register management, serving as a foundation for further studies into more complex architectural designs such as pipelining, caching, and memory hierarchy.

In professional environments, understanding these details is critical for tasks ranging from low-level programming (such as assembly language and system programming) to high-level system design and optimization. Knowledge of how these registers function can aid troubleshooting, performance analysis, and the design of more efficient hardware-software interfaces.

Future Directions in Register Design

As computing demands increase, register design continues to evolve. Innovations in quantum computing, neuromorphic designs, and other cutting-edge fields may one day redefine how data is managed at the lowest levels of computation. Nonetheless, the principles governing the MAR and MDR remain relevant in understanding these new paradigms.

Researchers and practitioners alike study these registers not only to enhance current technology but also to explore novel methods for data transfer and processing in next-generation computing systems. Their continual relevance underscores the timeless nature of their design philosophy.

References

- Memory address register - Wikipedia

- Different Classes of CPU Registers - GeeksforGeeks

- Memory Data Register - Vaia

- Memory Data Register CPU - Algo Education

- Memory Address Register - StudySmarter

Recommended Related Queries

- How does the CPU communicate with RAM through registers?

- What are the different types of registers in computer architecture?

- How do buffering and caching improve data transfer efficiency?

- What are the roles of control signals in memory access operations?

- How will modern architectural advancements affect register design?

Last updated March 14, 2025